# Device Register Map

The device register map supports the Compact 2-port IO-Link Master for Modbus (R45C-2K-MQ) and the Compact 4-port IO-Link Master for Modbus (R90C-4K-MQ).

## Supported Function Codes

| Function Code | Name                     | Max Message Size |

|---------------|--------------------------|------------------|

| 3 (0x03)      | Read Holding Register    | 250 bytes        |

| 6 (0x06)      | Write Single Register    | 2 bytes          |

| 16 (0x10)     | Write Multiple Registers | 246 bytes        |

| 23 (0x17)     | Read and Write Registers | 246 bytes        |

# Modbus Configuration

Modbus configuration is used for changing communications settings on converter.

| Registers | Parameter                                                                               | Access | Default |

|-----------|-----------------------------------------------------------------------------------------|--------|---------|

| 40601     | Baud Rate:                                                                              | r/w    | 19200   |

|           | 9600 = 0<br>19200 = 1<br>38400 = 2                                                      |        |         |

| 40602     | Parity:                                                                                 | r/w    | None    |

|           | None = 0<br>Odd = 1<br>Even = 2                                                         |        |         |

| 40603     | Address                                                                                 | r/w    | 1       |

| 40604     | Reserved (cannot be read or written)                                                    | None   | -       |

| 40605     | Restore Factory Configuration:<br>No Operation = 0<br>Restore Factory Configuration = 1 | w/o    | _       |

# Identification Information

| Register    | Parameter                                                                                                                                              | Access |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 40001       | Vendor ID                                                                                                                                              | r/o    |

| 40002-40003 | Master ID                                                                                                                                              | r/o    |

| 40004       | Master Type (see IO-Link Specification V1.1.3 table 29 for enumeration)                                                                                | r/o    |

| 40005       | Features_1:<br>Bit 0: DeviceParBatch (SMI_ParamWriteBatch)<br>Bit 1: DeviceParBatch (SMI_ParamReadBatch)<br>Bit 2: PortPowerOffOn (SMI_PortPowerOffOn) | r/o    |

| 40006       | Number of Supported Channels                                                                                                                           | r/o    |

| 40007-40014 | Port Type [n] <sup>1</sup> (see Table E.2 - MasterlDent from IO-Link<br>Interface Specification V1.1.3 for enumerations)                               | r/o    |

| 40015       | Total Max Power Supply (in units of 0.1 A)                                                                                                             | r/o    |

| 40016-40023 | Max Power Supply (in units of 0.1 A)                                                                                                                   | r/o    |

| 40024       | Revision                                                                                                                                               | r/o    |

| 40025-40040 | Vendor Name                                                                                                                                            | r/o    |

| 40041-40056 | Product Name                                                                                                                                           | r/o    |

| 40057-40088 | Vendor URL                                                                                                                                             | r/o    |

| 40089-40120 | Manual URL                                                                                                                                             | r/o    |

| 40121-40122 | Firmware P/N 1                                                                                                                                         | r/o    |

| 40123       | Firmware Version 1                                                                                                                                     | r/o    |

| 40124       | Firmware Build Number <sup>1</sup>                                                                                                                     | r/o    |

| 40125-40140 | Application Specific Tag                                                                                                                               | r/w    |

| 40141-40156 | Function Tag                                                                                                                                           | r/w    |

| 40157-40172 | Location Tag                                                                                                                                           | r/w    |

<sup>1</sup> Normally available as an input register. Added to holding registers so it can be accessed if input registers are not supported.

# Multi-Port Support

All register maps shown below are specific to port 1. For multi-port adapters, each port is given its own register range within the holding register space.

| Registers   | Port   |

|-------------|--------|

| 41001-41999 | Port 1 |

| 42001-42999 | Port 2 |

| 43001-43999 | Port 3 |

| 44001-44999 | Port 4 |

| 45001-45999 | Port 5 |

| 46001-46999 | Port 6 |

| 47001-47999 | Port 7 |

| 48001-48999 | Port 8 |

For a given register, the starting address of the port can be applied to determine the register address for the new port. For example, the calculation below demonstrates how to find the address of the process data output for port 8.

| Equivalent Port 1 Register | Port | Port Starting Register | Offset | New Register |

|----------------------------|------|------------------------|--------|--------------|

| 41051                      | 1    | 41001                  | 50     | 41051        |

| 41051                      | 8    | 48001                  | 50     | 48051        |

### Port Status

Information regarding the connected device is provided by the following holding registers. When a new device is connected, all data attempts to be read from the device. Unsupported commands read as an empty string.

Register endian swapping is not performed on the string values. The byte order of the data payload matches the byte-order from the device. Writing to these registers results in an error.

| Registers   | Parameter                                                   | Access |

|-------------|-------------------------------------------------------------|--------|

| 41501       | Port Mode 2                                                 | r/o    |

| 41502       | PortQualityInfo:                                            | r/o    |

|             | Bit0: Process Data In Valid<br>Bit1: Process Data Out Valid |        |

| 41503       | IO-Link Revision                                            | r/o    |

| 41504       | Com Mode:                                                   | r/o    |

|             | COM1 = 0<br>COM2 = 1<br>COM3 = 2                            |        |

| 41505       | Master Cycle Time                                           | r/o    |

| 41506       | Process Data Input Size (bytes)                             | r/o    |

| 41507       | Process Data Output Size (bytes)                            | r/o    |

| 41508       | Vendor ID (for pre 1.1 devices)                             | r/o    |

| 41509-41510 | Device ID (for pre 1.1 devices)                             | r/o    |

| 41511       | Min Cycle Time                                              | r/o    |

| 41512-41543 | Vendor Name                                                 | r/o    |

| 41544-41575 | Vendor Text                                                 | r/o    |

| 41576-41607 | Product Name                                                | r/o    |

| 41608-41639 | Product ID                                                  | r/o    |

| 41640-41671 | Product Text                                                | r/o    |

| 41672-41679 | Serial Number                                               | r/o    |

| 41680-41711 | Hardware Revision                                           | r/o    |

| 41712-41743 | Firmware Revision                                           | r/o    |

| 41744-41759 | Application Specific Tag                                    | r/o    |

| 41760-41775 | Function Tag                                                | r/o    |

| 41776-41791 | Location Tag                                                | r/o    |

| 41792-41823 | Profile Characteristic                                      | r/o    |

<sup>2</sup> Enumerations (from IO-Link Interface Spec V1.1.3, Table E.4):

- 0: NO\_DEVICE

- 1: DEACTIVATED

- 2: PORT\_DIAG

3: PREOPERATE

- 4: OPERATE

- 5: DI\_C/Q

- 6: DO\_C/Q

# Process Data Input

If no device is connected, all registers read as 0. Unused process data bytes also read as 0.

Data bytes are not register endian swapped. The byte order of the data payload matches the byte-order from the device.

Writing to these registers results in an error.

| Registers   | Parameter                                                                                                                                                                                                                                 | Access |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 41001       | Port Status:                                                                                                                                                                                                                              | r/o    |

|             | Bit0 = Connected?<br>Bit1 = Process Data Valid?<br>Bit2 = Event Pending?<br>Bit3 = Ready for ISDU?<br>Bit4 = Pin4 SIO State<br>Bit5 = Pin2 SIO State<br>Bit6-7 = Pin4 Mode:<br>SDCI Mode = 0<br>SIO Input Mode = 1<br>SIO Output Mode = 2 |        |

|             | Bit6-10 = Pin2 Mode:           Disabled = 0           Input Normal = 1           Output = 2           Diagnostic Input = 3           Inverted Input = 4                                                                                   |        |

| 41002-41017 | Data                                                                                                                                                                                                                                      | r/o    |

Discrete modes can be added as input process data so that a reset of the master can be detected when discrete output mode is being used. After reset, the master returns to SDCI Mode on Pin4 and Disabled on Pin2.

### Process Data Output

Data bytes are not register endian swapped. The byte order of the data payload matches the byte-order written to the device.

A read of this parameter returns the most recent process data output written to the adapter.

The process data out behavior if a sensor is disconnected and reconnected is undefined.

| Registers   | Parameter                                                                   | Access |

|-------------|-----------------------------------------------------------------------------|--------|

| 41051       | Bit0 = IsValid,<br>Bit1 = Pin4 Output State 3<br>Bit2 = Pin2 Output State 3 | r/w    |

| 41052-41067 | Data                                                                        | r/w    |

### ISDU (Index/Subindex) Data

ISDU data operations are based on a request/response model. First the request is written to the adapter, and then the response is read. The request is non-blocking, so the status register of the response must be polled to determine when the request has been completed.

Any write to any of the request registers triggers the request. If the write is to be broken up into multiple write operations, a NOP opcode should first be written to prevent the request from being handled until all data has been written to the adaptor.

The result register contains an indication of whether the requested operation succeeded or failed. In the case of a failure, the error code returned by the device is not available.

Data bytes are not register endian swapped. The byte order of the data payload matches the byte-order read from/written to the device.

### ISDU Request Register Block

For a write, the data length must match the required data length being written to the device. For a read, the length is a don't care; that is, the returned length of the read is not checked by the adapter.

For a write, the data contains the data to be written to the sensor. For a read, the data is a don't care.

| Registers   | Parameter                        | Access |

|-------------|----------------------------------|--------|

| 41301       | Operation:                       | r/w    |

|             | NOP = 0<br>Read = 1<br>Write = 2 |        |

| 41302       | Index                            | r/w    |

| 41303       | Subindex (max = 255)             | r/w    |

| 41304       | Data Length (max = 238)          | r/w    |

| 41305-41423 | Data                             | r/w    |

#### ISDU Response Register Block

The Operation, Index, and Subindex match the value from the most recent request.

For a write, the length matches the length of data written. For a read, the length contains the number of bytes returned from the device.

For a write, the data contains the data written to the device. For a read, the data contains the data read from the device.

<sup>&</sup>lt;sup>3</sup> If pins are not configured in SIO output mode, writes are ignored and reads are returned as 0.

If a failure has occurred (Status == Failure), then the Data Length is set to 2. Data[0] contains the Error Code while Data[1] contains the Additional Code. An Error Code of 0 represents an internal error within the master module, while other Error Codes are defined in Annex C of the IO-Link Interface Specification.

| Registers   | Parameter                                                           | Access |

|-------------|---------------------------------------------------------------------|--------|

| 41101       | Operation (see Request for opcodes)                                 | r/o    |

| 41102       | Status:<br>NOP = 0<br>In Progress = 1<br>Success = 2<br>Failure = 3 | r/o    |

| 41103       | Index                                                               | r/o    |

| 41104       | Subindex (max = 255)                                                | r/o    |

| 41105       | Data Length (max = 238)                                             | r/o    |

| 41106-41224 | Data                                                                | r/o    |

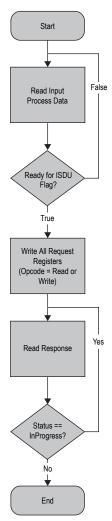

ISDU Read/Write in Single Register Write

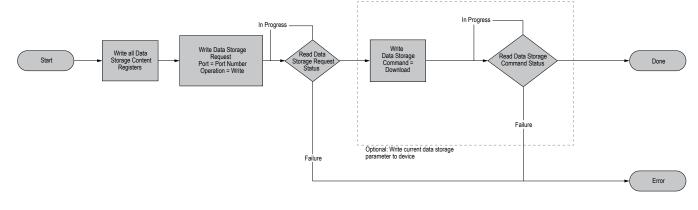

The flowchart documents how to perform an ISDU read/write operation using a single *Write Multiple Registers* Modbus command of the *ISDU Request* register block.

The request is dispatched to the connected device after the request is written. For a read operation, at the end of the sequence, the response data contains the data returned from the device.

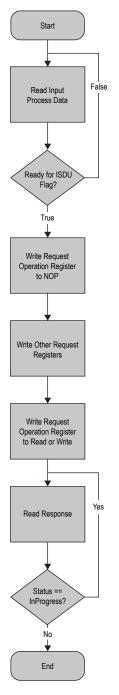

### ISDU Read/Write in Multiple Register Writes

The flowchart documents how to perform an ISDU read/write operation using multiple *Write Multiple Registers* or *Write Single Register* Modbus commands of the *ISDU Request* register block.

The request is not dispatched to the connected device until the opcode is written to read/write. For a read operation, at the end of the sequence, the response data contains the data returned from the device.

# Port Configuration

| Registers   | Parameter                                         | Access |

|-------------|---------------------------------------------------|--------|

| 41851       | Port Mode 4                                       | r/w    |

| 41852       | Validation&Backup <sup>5</sup>                    | r/w    |

| 41853       | I/Q behavior <sup>6</sup>                         | r/w    |

| 41854       | PortCycleTime (reserved): 0 = As Fast As Possible | r/w    |

| 41855       | Vendor ID                                         | r/w    |

| 41856-41857 | Device ID                                         | r/w    |

| Registers | Parameter                                                          | Access |

|-----------|--------------------------------------------------------------------|--------|

| 41858     | Pin4 Extra Configuration                                           | r/w    |

|           | <b>Bit0-1: Output Type:</b><br>Push-Pull = 0<br>PNP = 1<br>NPN = 2 |        |

|           | Bit2: Z 8<br>Normal Input = 0<br>Diagnostic Input = 1              |        |

|           | Bit3: 7<br>Non-inverted Input = 0<br>Inverted Input = 1            |        |

|           | Bit4: 9<br>Input Type 1 = 0<br>Input Type 2 = 1                    |        |

| 41859     | Pin2 Extra Configuration: 78                                       | r/w    |

|           | Normal = 0<br>Diagnostic Input = 1<br>Inverted Input = 2           |        |

If Port Mode is set to IOL\_AUTOSTART (default), the master ignores the Vendor ID and Device ID of the connected device.

If Port Mode is set to IOL\_MANUAL, the master will attempt to write the Device ID into the device at connection. If the Vendor ID and Device ID are not supported by the device, the master will not connect.

This value is non-volatile and is stored to EEPROM and persisted across adapter power cycles. After a write to any register in this block, the port is reset to apply the new configuration settings.

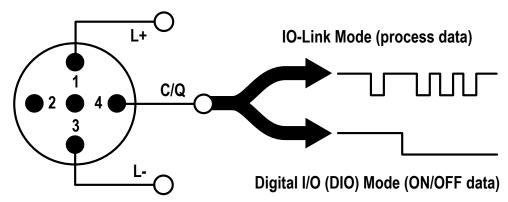

### **Operating Modes**

The operating mode can be configured for any port on the IO-Link master. The following modes can be used:

#### Deactivated

Use deactivated mode for any unused IO-link master ports if a device is not connected.

#### **IO-Link Manual**

The IO-Link master only connects IO-Link devices that have a certain vendor ID and device ID (1: IOL\_MANUAL).

#### **IO-Link Autostart**

The IO-Link master connects to every connected IO-Link device (2: IOL\_AUTOSTART).

### **Digital Input**

The IO-Link port functions as a standard digital input (3: DI\_C/Q).

#### **Digital Output**

The IO-Link port functions as a standard digital output (4: DO\_C/Q).

Figure 1. Operating modes

4 Enumerations (from IO-Link Interface Spec V1.1.3, Table E.3):

- 0: DEACTIVATED (SM: INACTIVE Port is deactivated; input and output Process Data are 0; Master shall not perform activities at this port)

- 1: IOL\_MANUAL (SM: CFGCOM Target Mode based on user defined configuration including validation of RID, VID, DID)

- 2: IOL\_AUTOSTART (SM: AUTOCOM Target Mode w/o configuration and w/o validation of VID/DID; RID gets highest revision the Master is supporting; Validations: NO\_CHECK)

- 3: DI\_C/Q (Pin 4 at M12) (SM: DI Port in input mode SIO)

- 4: DO\_C/Q (Pin 4 at M12) (SM: DO Port in output mode SIO)

- 5 Enumerations (from IO-Link Interface Spec V1.1.3, Table E.3):

- 0: No Device check

- 1: Type compatible Device V1.0 2: Type compatible Device V1.1

- 3: Type compatible Device V1.1, Backup + Restore

- 4: Type compatible Device V1.1, Restore

- 6 Enumerations (from IO-Link Interface Spec V1.1.3, Table E.3):

- 0: Not supported

- 1: Digital Input

- 2: Digital Output

- Don't care if not in SIO Input mode

- If configured as a diagnostic input, then the LED turns red when the input is in the inactive state. This can be used to indicate a failure of the connected device.

- Type 1 supports IEC 61131-2 Type 1 input voltage levels. Type 2 supports IEC 61131-2 Type 2 and Type 3 input voltage levels.

# Replacing an IO-Link Device During Operation (Backup/Restore Mode)

Replacing an IO-Link device during operation is common, and inadvertent changes to device settings can cause operational problems and downtimes. Operating personnel without special knowledge or tools can replace IO-Link devices quickly and without errors.

When the backup function of the IO-Link master is used, the IO-Link master automatically provides the saved parameters to the new device after replacement. This makes IO-Link device replacement seamless in IO-Link applications. Another common industry term for this function is *data storage mode*.

#### . Backup+Restore Mode

If a port on the IO-Link master is set to Backup+Restore, then the new device added to the IO-Link port takes in the same device configuration as the device that was just replaced, as the IO-Link master had stored the last configuration change by a backup (3: Type compatible Device V1.1, Backup + Restore).

#### . Restore

If the port on the IO-Link master port is set to Restore, then the new device takes in the configuration according the settings saved in the master at the time of the last backup. Because possible configuration changes were not saved in the master, a different behavior from the previous one before the replacement may occur (4: Type compatible Device V1.1, Restore).

### **IO-Link Events**

If an event is pending, the *Event Pending* flag is set in the process data input register block. If a user is not concerned with IO-Link events, they can ignore the state of this flag.

Events are read via the Event status register block:

| Registers | Parameter                                                   | Access |

|-----------|-------------------------------------------------------------|--------|

| 41901     | Count (max = 10)                                            | r/o    |

| 41902     | Mode[0]:                                                    | r/o    |

|           | None = 0<br>SingleShot = 1<br>Disappears = 2<br>Appears = 3 |        |

| 41903     | Туре[0]:                                                    | r/o    |

|           | None = 0<br>Notification = 1<br>Warning = 2<br>Error = 3    |        |

| 41904     | Code[0]                                                     | r/o    |

| 41905     | Mode[1] 10                                                  | r/o    |

| 41906     | Type[1] 10                                                  | r/o    |

| 41907     | Code[1] 10                                                  | r/o    |

Events are stored in a FIFO buffer, where Mode[0] is the oldest event in the queue. If a new event is received when the queue is full, the oldest event in the queue is shifted out.

After an event has been read, it can be cleared by writing its event code to the Clear Event Register:

| Registers | Parameter  | Access |

|-----------|------------|--------|

| 41951     | Event Code | w/o    |

<sup>10</sup> Repeats for 10 total supported events

### IO-Link Event Processing

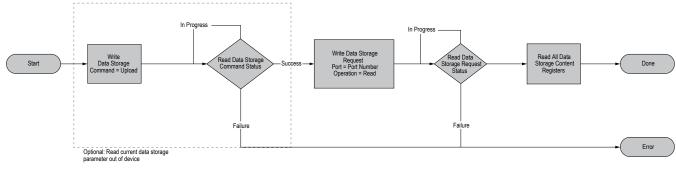

### Data Storage

The data storage configuration is set as part of the *Port Configuration* object. The operations can also be triggered manually using the *Data Storage Command* register:

| Registers | Parameter                                          | Access |

|-----------|----------------------------------------------------|--------|

| 41981     | Data Storage Command:                              | w/o    |

|           | NOP = 0<br>Upload = 1<br>Download = 2<br>Clear = 3 |        |

The command is executed immediately upon writing the command.

The status of the requested data storage command can be accessed via the Data Storage Command Status register:

| Registers | Parameter                                                | Access |

|-----------|----------------------------------------------------------|--------|

| 41991     | Data Storage Command Status:                             | r/o    |

|           | NOP = 0<br>In Progress = 1<br>Success = 2<br>Failure = 3 |        |

### Data Storage Content

The following registers are outside the normal 40000-49999 range of holding registers. They are only available through direct addressing, and not through Modicon.

| Registers | Parameter      | Register Description             |

|-----------|----------------|----------------------------------|

| 50000     | Port Selection | _                                |

| 50001     |                | 0 = NOP<br>1 = Read<br>2 = Write |

| Registers | Parameter | Register Description                                     |

|-----------|-----------|----------------------------------------------------------|

| 50002     | Status 11 | 0 = NOP<br>1 = In Progress<br>2 = Success<br>3 = Failure |

Reading/writing the data storage contents does not trigger an upload/download to/from the connected device. To do so, write the desired operation to the appropriate port's Data Storage Command register.

| Registers   | Parameter            |

|-------------|----------------------|

| 50100-51123 | Data Storage Content |

The data storage content is unpopulated (read as 0) prior to performing a data storage read operation.

While the master supports storing separate data storage contents per port, a single buffer is shared for all ports for communications purposes. To support data storage content over multiple ports, the port must be specified in the Data Storage Request registers prior to reading/writing the contents.

#### Reading from Data Storage Content

#### Writing from Data Storage Content

### Alias Registers

There are two register sets that are part of the holding registers.

### Read-Only Alias Registers

This set is the user-configurable alias configuration registers:

| Registers   | Parameter                        | Access |

|-------------|----------------------------------|--------|

| 40701-40768 | Read/Only Alias Register Address | r/w    |

Each register in this section contains the 16-bit register address for the corresponding alias holding register, which is readable in the alias register space:

| Registers   | Parameter                | Access |

|-------------|--------------------------|--------|

| 40501-40568 | Read/Only Alias Register | r/o    |

When reading an alias register, the data in the register is filled with the contents of the address that are present in the corresponding alias configuration register. The address can be stored in either direct or modicon addressing. Note that all aliased registers are read-only, and it is not possible to write to an alias register.

Any alias registers that are configured to an unsupported register address, or where the read operation fails for some other reason, returns as a zero when read.

11 Writes to this register are ignored.

#### Example

Consider reading the process data state registers for all four ports in a single read operation. In this example, the holding registers are configured with the data below:

| Register | Value | Register Description            |

|----------|-------|---------------------------------|

| 40701    | 41001 | Port 1 input process data state |

| 40702    | 42001 | Port 2 input process data state |

| 40703    | 43001 | Port 3 input process data state |

| 40704    | 44001 | Port 4 input process data state |

If the alias registers are read, then they will contain the following register contents:

| Register | Value | Register Description            |

|----------|-------|---------------------------------|

| 40501    | 41001 | Port 1 input process data state |

| 40502    | 42001 | Port 2 input process data state |

| 40503    | 43001 | Port 3 input process data state |

| 40504    | 44001 | Port 4 input process data state |

By default, the alias register is set-up to alias process data for all available ports into a consecutive register map. The alias configuration can always be restored to its factory default value by writing to the Restore Factory Configuration holding register (40605). The alias register space is sized to allow reading all input process data from a 4-port device.

#### **Read-Write Alias Registers**

This set is a series of alias registers with read-write access allowed:

| Registers   | Parameter                         | Access |

|-------------|-----------------------------------|--------|

| 40901-40968 | Read/Write Alias Register Address | r/w    |

Each register in this section contains the 16-bit register address for the corresponding alias holding register, which is readable in the alias register space:

| Registers   | Parameter                 | Access |

|-------------|---------------------------|--------|

| 40801-40868 | Read/Write Alias Register | r/w    |

By default, the read-write alias registers are configured to point to the output process data for each port. The register space is sized to allow for aliasing all output process data for a 4-port device.

If writing to an alias register fails (for example, if the aliased register is not writeable), then the write operation of the alias registers will NACK. A register value that is set to 65535 is always read as 0, and no write operation will be attempted.